This article was downloaded by: [University of California, San Diego]

On: 07 August 2012, At: 12:07 Publisher: Taylor & Francis

Informa Ltd Registered in England and Wales Registered Number: 1072954 Registered

office: Mortimer House, 37-41 Mortimer Street, London W1T 3JH, UK

# Molecular Crystals and Liquid Crystals

Publication details, including instructions for authors and subscription information:

http://www.tandfonline.com/loi/gmcl20

# Capacitance Parameter Extraction and Modeling for Amorphous Silicon Thin-Film Transistors

Sang-Kug Han  $^{\rm a}$  , Hoon Choi  $^{\rm a}$  , Kyo-Ho Moon  $^{\rm a}$  , Young-Seok Choi  $^{\rm a}$  , Sang-Hyuk Ryu  $^{\rm b}$  & Sie-Young Choi  $^{\rm c}$

<sup>a</sup> Panel Department, LG Display Company Ltd., 1007, Deogeun-ri Wollong-myeon, Paju-si, Gyeonggi-do, 413-811, Korea

<sup>b</sup> Department of Electronics Engineering, Daegu University, Gyeongbuk, 712-714, Korea

<sup>c</sup> School of Electronic and Electrical Engineering, Kyungpook National University, Korea

Version of record first published: 18 Oct 2011

To cite this article: Sang-Kug Han, Hoon Choi, Kyo-Ho Moon, Young-Seok Choi, Sang-Hyuk Ryu & Sie-Young Choi (2011): Capacitance Parameter Extraction and Modeling for Amorphous Silicon Thin-Film Transistors, Molecular Crystals and Liquid Crystals, 550:1, 66-75

To link to this article: <a href="http://dx.doi.org/10.1080/15421406.2011.600217">http://dx.doi.org/10.1080/15421406.2011.600217</a>

### PLEASE SCROLL DOWN FOR ARTICLE

Full terms and conditions of use: http://www.tandfonline.com/page/terms-and-conditions

This article may be used for research, teaching, and private study purposes. Any substantial or systematic reproduction, redistribution, reselling, loan, sub-licensing, systematic supply, or distribution in any form to anyone is expressly forbidden.

The publisher does not give any warranty express or implied or make any representation that the contents will be complete or accurate or up to date. The accuracy of any instructions, formulae, and drug doses should be independently verified with primary sources. The publisher shall not be liable for any loss, actions, claims, proceedings, demand, or costs or damages whatsoever or howsoever caused arising directly or indirectly in connection with or arising out of the use of this material.

Mol. Cryst. Liq. Cryst., Vol. 550: pp. 66-75, 2011 Copyright © Kyungpook National University ISSN: 1542-1406 print/1563-5287 online

DOI: 10.1080/15421406.2011.600217

# **Capacitance Parameter Extraction and Modeling** for Amorphous Silicon Thin-Film Transistors

SANG-KUG HAN,1 HOON CHOI,1 KYO-HO MOON,1 YOUNG-SEOK CHOI,1 SANG-HYUK RYU,2 AND SIE-YOUNG CHOI<sup>3,\*</sup>

<sup>1</sup>Panel Department, LG Display Company Ltd., 1007, Deogeun-ri Wollong-myeon, Paju-si, Gyeonggi-do, 413-811, Korea <sup>2</sup>Department of Electronics Engineering, Daegu University, Gyeongbuk, 712-714, Korea <sup>3</sup>School of Electronic and Electrical Engineering, Kyungpook National University, Korea

This paper presents modeling and parameter extraction of the capacitance characteristics of the inverted-staggered a-Si:H TFT in both the depletion and inversion regions of operation. The need for a model of the capacitance with variable gate-source or gate-drain bias is imperative for a robust circuit design. However, the previous model parameter expression is applied to the staggered a-Si:H TFT. In this paper, we investigated the capacitance characteristics and modeling using the new extracted method for the inverted staggered structure. The accuracy of the simulated curves using parameters extracted with the new procedure is verified with measured and calculated data.

Keywords Thin Film Transistor; a-Si:H transistor model; Kick-back Effect; Parameter Extraction; Voltage-Controlled Capacitance

#### Introduction

Hydrogenated amorphous silicon(a-Si:H) thin-film transistors (TFTs) are the most widely used switching devices in active matrix liquid crystal displays. AMLCDs have been applied to many information tools such as personal computers, PDAs, and picture displays. For these applications, accurate TFT models and reliable methods for parameter extraction are critical for circuit design. Shur et al. [1–5], Leroux, Khakzar et al., and other authors have presented several models for the different operational regimes of a-Si:H TFTs. They consist of the overlap capacitance (CGSO and CGDO), the oxide thickness (TOX), the dielectric constant of the oxide (EPSI) and the substrate layer (EPS) and the Zero-bias leakage current (IOL). Other parameters related to the trap distribution and intrinsic layer impurity concentration, as the Fermi level position (DEFO), the minimum density of deep states (GMIN) and the characteristic voltage for deep states (V0), can be estimated from physical ideas and procedures previously reported.

However a universal model for capacitance parameter has two problems. First, the numerical formula of the conventional capacitance parameters is applied to the staggered

<sup>\*</sup>Corresponding author.. E-mail: sychoi@ee.knu.ac.kr

and symmetric a-Si:H TFT. It is different from the inverted staggered and non-symmetric a-Si:H TFT which is the most widely employed structure. Second, there are no parameters which can control the slope and accurate value of capacitance-voltage characteristics.

In this paper, the C-V characteristics in a-Si:H TFTs with inverted staggered structures were investigated by using the AC voltage at high frequencies and moderate measurement temperatures. Also, a new method was presented to extract the capacitance parameter of these structures.

# **Experimental**

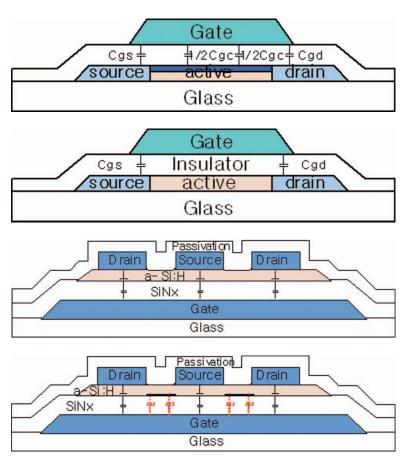

Scheme 1 shows a cross-sectional view of (a) the staggered and (b) the inverted staggered a-Si:H TFT structure for operating voltage. These model structures were presented for the capacitance characteristics of the staggered and the inverted staggered a-Si:H TFT in both depletion and inversion regions of operating voltage.

**Scheme 1.** Depletion mode of the staggered a-Si:H TFT. Inversion mode of the staggered a-Si:H TFT. (a) Depletion mode of the inverted staggered a-Si:H TFT. Inversion mode of the inverted staggered a-Si:H TFT.

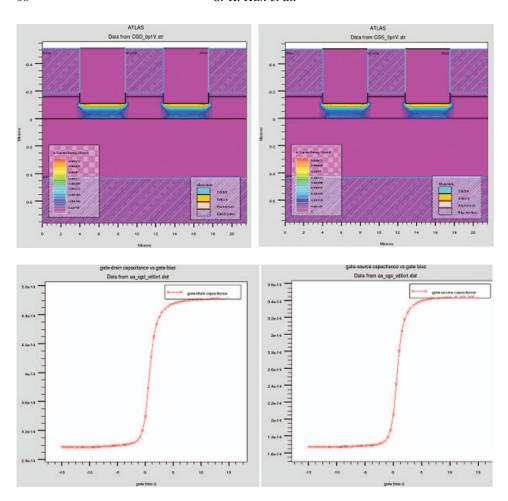

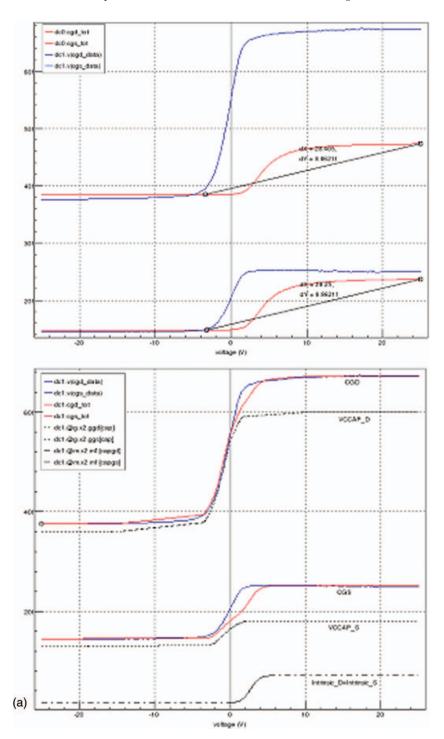

Figure 1 shows a physically-based, two-dimensional simulation of the inverted staggered a- Si:H TFT structure. Fig. 1 (a) shows a cross sectional view of a-Si:H for electron

**Figure 1.** Physically-based, two-dimensional Simulation and of the inverted staggered a-Si:H TFT structure.

current density and (b) shows the capacitance versus voltage characteristics for amorphous silicon transistor when the gate bias is applied at 21°C and 10kHz.

#### **Fabrication**

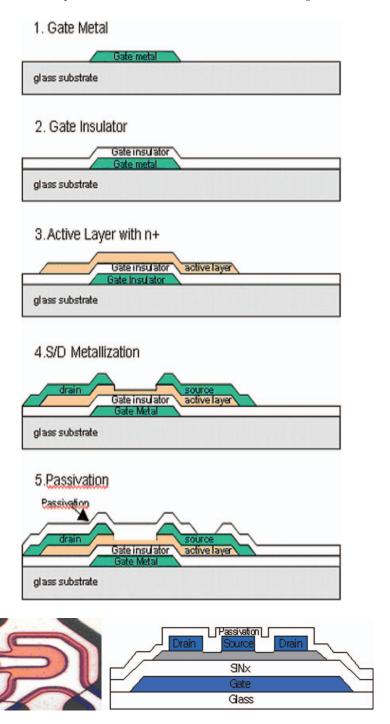

Figure 2 shows an enlarged top view and cross sections of the inverted-staggered a-Si:H TFT used in this study. The pattern-defined channel length(L) and width(W) were 4.78 um and 30 um, respectively. The pattern-defined gate to source and gate to drain overlap areas, AreaS and AreaD, respectively, were 44 um<sup>2</sup> and 174 um<sup>2</sup>. This structure was fabricated by using the following process. First, a copper gate electrode was deposited on a glass substrate by using a reactive ion sputtering and was then patterned by using standard photolithography. After that, the a-SiN:H layer, a-Si:H layer and n+ a-Si:H layers were deposited consecutively in a high- vacuum plasma enhanced chemical vapor deposition(PECVD). Thickness of the a-SiN:H, a-Si:H and n+ a-Si:H layers were 4300 Å, 1600 Å and 300 Å, respectively. The metal layer of source and drain was deposited on 3200 Å by using reactive

Figure 2. The process flow chart of the inverted staggered a-Si:H TFT.

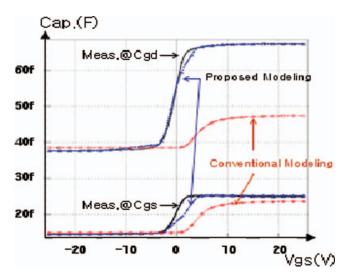

**Figure 3.** Measured and Simulated C-V characteristics of the inverted stagger a-Si:H TFT about the conventional and the proposed capacitance modeling at 21°C and 50 kHz.

ion sputtering. The a-Si:H, n+ a- Si:H and metals were then patterned. Finally, an a-SiNx passivation layer was deposited and patterned.

#### Measurements

The C-V characteristics of fabricated a-Si:H TFT were measured using an HP 4284A analyzer. Figure 3 (a) shows the variations of Cgs and Cgd without pin capacitance in both the inversion and depletion range of the gate voltage at 27°C and 50 kHz. The numerical formula of the conventional capacitance parameters was applied to the staggered and symmetric a-Si:H TFT. It is different from the inverted staggered and non symmetric a-Si:H TFT which is the most widely employed structure.

#### Results and Discussion

Figure 4 (a) shows the conventional and the proposed capacitance simulation results. In the depletion region, the numerical Cgd and Cgs for a universal model structure can be written as:

$$Cgs\_dep\_model = CGSO * W\_effoverlap$$

(1)

$$CGSO = (METO + LD) \times \frac{(EPSI \times \varepsilon_O)}{TOX}$$

(2)

Here CGSO is the source overlap capacitance factor(F/m), METO is the Fringe Factor, and LD is the lateral diffusion into a channel from source and drain. In addition EPSI is the relative dielectric constant of the gate insulator, and TOX is the thickness of the gate insulator. The a- Si:H permittivity wasn't reflected in this equation. Therefore, the Cgs and Cgd were increased in the depletion region. The calculated Cgs and Cgd for a conventional structure will simply be the geometric overlap capacitance. In the depletion range, Cgs and

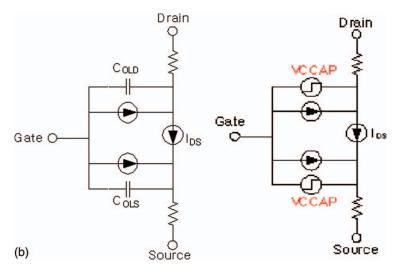

**Figure 4.** (a) Simulated C-V Characteristics and (b) Equivalent circuits of the conventional TFT model using geometric capacitance per unit area and the proposed TFT model using voltage controlled capacitance. (*Continued*)

Figure 4. (Continued)

Cgd can be written as:

$$Cgs-dep-cal. = Cmin \times W \times \Delta L_S$$

(3)

$$Cgd-dep-cal. = Cmin \times W \times \Delta L_D$$

(4)

$$C_{\min} = 1/[(d_i/\varepsilon_i) + (d_{a-Si}/\varepsilon_{a-Si})]$$

(5)

In the inversion range, Cgs and Cgd can be written as:

$$Cgs-inv.-cal = Cmax \times W \times (\Delta L_s + \delta L_s)$$

(6)

$$Cgd-inv.-cal = Cmax \times W \times (\Delta L_D + \delta L_D)$$

(7)

$$C_{\text{max}} = 1/[(d_i/\varepsilon_i)] \tag{8}$$

Here di, da-Si,  $\varepsilon i$ , and  $\varepsilon_{a-Si}$  are thicknesses and the permittivity of the gate insulator and a Si:H layer. Also,  $\delta Ls$  is the effective channel length of the source side, and  $\delta Ls$  is the effective channel length of the drain side. That is,  $\delta Ls + \delta L_D$  is equal to the channel Length L. However, the calculated data are different from the simulated data. This is because it is applied to the numerical formula of the staggered and symmetric a-Si:H TFT. That is, it is difficult to increase the capacitance accuracy in the depletion and the inversion region. To solve these problems, the capacitance characteristics of inverted staggered a-Si:H TFT were compensated using voltage-controlled capacitance when it happens the variation of the density of state(DOS). The Cgs and Cgs with voltage-controlled capacitance can be written as:

$$Cgs-sim. = Cgs-vccap + Cintrinsic or Coff$$

(9)

$$Cgd$$

-sim. =  $Cgd$ -vccap + Cintrinsic or Coff (10)

Here Cgs-vccap is the voltage-controlled capacitance for compensating Cgs-sim and Cgd-sim. Cintrinsic is the intrinsic capacitance of Cgd or Cgs in the inversion region. Coff can

**Table 1.** Capacitance parameter Extraction Results of the staggered and the inverted staggered a-Si:H TFT

| Sample                               | a-Si:H TFT     |

|--------------------------------------|----------------|

| Conventional Model<br>Proposed Model | CGD0 = 1.23e-9 |

be written as CFri.(Fringe cap.) The capacitance extraction results with voltage controlled capacitance were shown in Table 1.

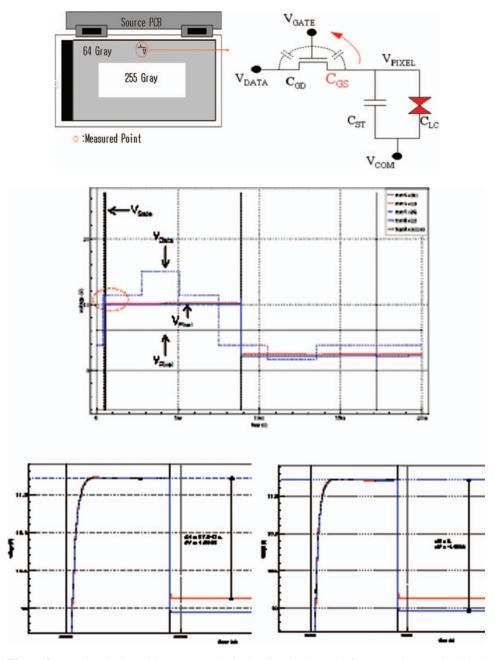

Figure 5 shows the simulated results for the TFT-LCD panel at 21°C and 120Hz. This focuses specifically on the delta-Vp( $\Delta$ Vp) for SXGA. The result of the UTMOST and SMARTSPICE simulators show the delta-Vp of the proposed model has been increased by 0.1362V for the conventional structure. The delta-Vo can be written as:

$$\Delta Vp = \frac{Cgs}{Cgs + Clc + Cst} \tag{11}$$

## **Conclusions**

Although, there are many TFT devices which have been demonstrated using a-Si:H technology, it is difficult to define the accurate capacitance characteristics using the conventional model. One of the goals of this thesis is to increase the capacitance accuracy using the proposed model. The voltage controlled model has been matched by 90% for the Cgs and

**Figure 5.** (a) One pixel model structure and (b) the simulated results for TFT-LCD panel at  $21^{\circ}$ C and 120 Hz. Especially, focusing on the delta-Vp( $\Delta$ Vp) for SXGA.

Cgd capacitance compared to the conventional model. The simulated results for TFT-LCD are described, especially focusing on the delta-Vp ( $\Delta$ Vp) for SXGA. The delta-Vp for the conventional structure and the voltage controlled structure was 1.2696V and 1.4058V, respectively.

# References

- [1] M. Shur and M. Hack. (1984). J. Appl. Phys., 55, 10, 3831–3842.

- [2] M.S. Shur, H.C. Slade, M.D. Jacunski, A.A. Owusu, and T. Ytterdal. (1997). J. Electrochem. Soc., 144, 8, 2833–2839.

- [3] M. Shur, M. Hack, and J. G. Shaw. (1989). J. Appl. Phys., 66, 7, 3371–3380.

- [4] P. Servati and A. Nathan, A. J. Snell. (2002). J. Vac. Sci. Technol. A, 1038–1042.

- [5] R.A. Street and M. J. Thompson. (1984). Appl. Phys. Lett. 45, 7, 769–771.